Η 대만 경제 신문 그는 주장한다 TSMC 최종 폐기를 위해 중요한 내부 발견을 달성했습니다. 리소그래피 기술 2nm.

Σ간행물에 따르면 이 이정표를 통해 TSMC는 2년 초기 생산 "위험 생산" 2023nm 구현에 대해 낙관적.

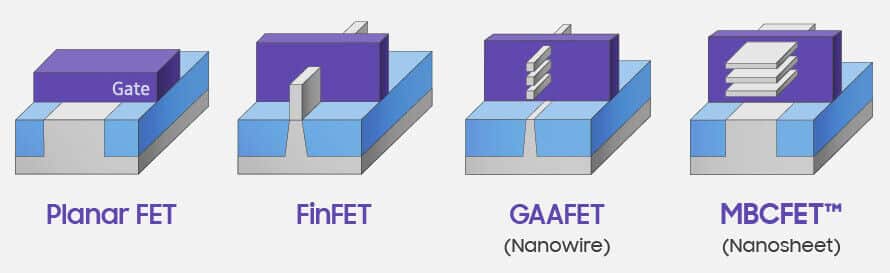

여전히 인상적인 보고서는 TSMC, 새로운 MBCFET(다중 브리지 채널 전계 효과) 트랜지스터를 위해 FinFet 기술 포기 GAA(Gate-All-Around) 기술을 기반으로 합니다. 이 중요한 발견이 온다 2nm 리소그래피 개발을 위한 길을 닦는 것을 목표로 하는 TSMC에서 실내 팀을 만든 지 XNUMX년 후.

MBCFET 기술은 나노와이어 전계 효과 트랜지스터를 "확산"하여 나노시트가 되도록 함으로써 GAAFET 아키텍처를 확장합니다. 주요 아이디어는 전계 효과 트랜지스터를 XNUMXD로 만드는 것입니다.

이 새로운 보완 금속 산화물 반도체 트랜지스터는 회로 제어를 개선하고 누설 전류를 줄일 수 있습니다. 이 디자인 철학은 배타적이지 않습니다. TSMC - 삼성 리소그래피 기술에서 이 디자인의 변형을 개발할 계획입니다. 3 nm의.

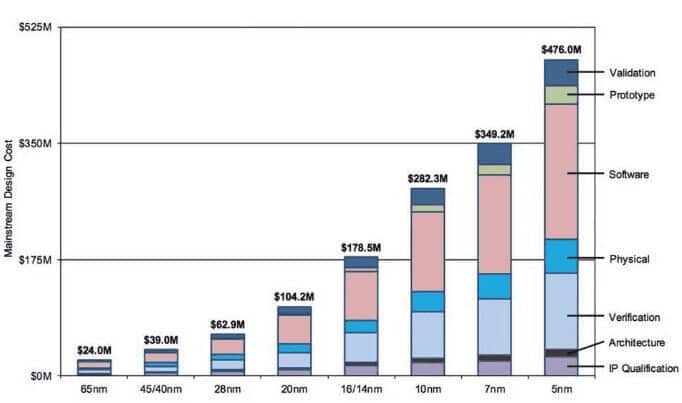

평소와 같이, 칩 제조 규모의 추가 축소는 막대한 비용을 초래합니다.. 특히 5nm 리소그래피의 개발비는 이미 476억 XNUMX만 달러에 달한 반면, 삼성은 이 기술이 3nm의 GAA 500억 달러가 넘는 비용이 들 것입니다. 물론 석판화의 발달 2 nm의, 이 금액을 초과합니다…

잊지말고 따라해보세요 Xiaomi-miui.gr 에 구글 뉴스 모든 새로운 기사에 대해 즉시 알려드립니다!

잊지말고 따라해보세요 Xiaomi-miui.gr 에 구글 뉴스 모든 새로운 기사에 대해 즉시 알려드립니다!